# 曜凌光電股份有限公司

住址: 42878 台中市大雅区科雅路 25 號 5F

WEB: <u>http://www.Raystar-Optronics.com</u>

5F., No.25, Keya Rd., Daya Dist., Taichung

E-mail: sales@raystar-optronics.com

City 428, Taiwan

Tel:886-4-2565-0761

Fax : 886-4-2565-0760

## RC1602B4-LLH-JWV

# **SPECIFICATION**

### CUSTOMER:

### APPROVED BY

PCB VERSION

### DATE

FOR CUSTOMER USE ONLY

| SALES BY      | APPROVED BY | CHECKED BY | PREPARED BY |

|---------------|-------------|------------|-------------|

|               |             |            |             |

|               |             |            |             |

| Release DATE: |             |            |             |

# **Revision History**

| VERSION | DATE       | REVISED PAGE NO. | Note                  |

|---------|------------|------------------|-----------------------|

| 0       | 2014/08/28 |                  | First issue           |

| А       | 2015/04/29 |                  | Correct               |

|         |            |                  | Recommended circuit   |

|         |            |                  | diagram               |

| В       | 2016/01/08 |                  | Modify IC information |

# Contents

- 1.General Specification

- 2. Module Classification Information

- 3.Interface Pin Function

- 4.Contour Drawing &Block Diagram

- 5. Character Generator ROM Pattern

- **6.Optical Characteristics**

- 7. Absolute Maximum Ratings

- **8.**Electrical Characteristics

- 9.Backlight Information

- 10.Reliability

- 11.Inspection specification

- 12.Precautions in use of LCD Modules

- 13. Material List of Components for RoHs

- 14.Recommendable Storage

- 15.Other

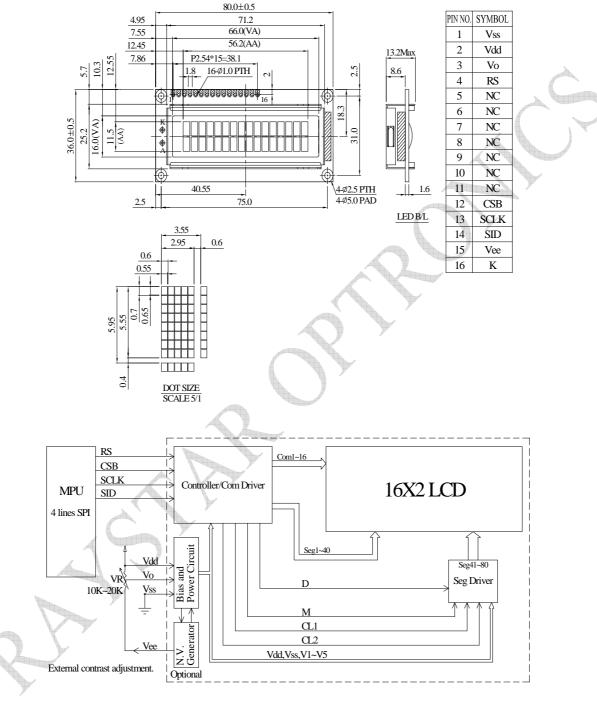

### **1.General Specification**

The Features is described as follow:

- Module dimension: 80.0 x 36.0 x 13.2 (max.) mm

- View area: 66.0 x 16.0 mm

- Active area: 56.20 x 11.5 mm

- Number of Characters: 16 characters x 2 Lines

- Dot size: 0.55 x 0.65 mm

- Dot pitch: 0.60 x 0.70 mm

- Character size: 2.95 x 5.55 mm

- Character pitch: 3.55 x 5.95 mm

- LCD type: VA Negative Transmissive

- Duty: 1/16

- View direction: 12 o'clock

- Backlight Type: LED, High light White

### **2.Module Classification Information**

| <u>R</u> | <u>C</u> | <u>1602</u> | <u>B4</u> | _ | L | L | <u>H</u>   | — | JWV |

|----------|----------|-------------|-----------|---|---|---|------------|---|-----|

| 1        | 2        | 3           | 4         |   | 5 | 6 | $\bigcirc$ |   | 8   |

| Item |                    | C                                                   | Descriptio | on            |                                        |

|------|--------------------|-----------------------------------------------------|------------|---------------|----------------------------------------|

| 1    | R : Raystar O      | ptronics Inc.                                       |            |               |                                        |

| 2    | Diaplay            | C: Character Type,                                  |            | T:TAB Type    |                                        |

| 2    | Display            | G : Graphic Type                                    |            | X:COG Type    |                                        |

| 3    | Number of dot      | s: Character 16 words, C                            | 2 Lines.   |               | (                                      |

| 4    | Serials code :     |                                                     |            |               |                                        |

|      |                    | P→TN Positive, Gray                                 |            | V→FSTN Ne     | egative, Blue                          |

|      |                    | N→TN Negative,                                      |            | T→FSTN Ne     | egative, Black                         |

|      |                    | L→VA Negative                                       |            | D→FSTN N      | egative (Double film)                  |

|      |                    | $H \rightarrow HTN$ Positive, Gray                  |            | F→FSTN Po     | ositive                                |

| 5    | LCD                | I→HTN Negative, Black                               |            | K→FSC Neg     | gative                                 |

|      |                    | U→HTN Negative, Blue                                |            | S→FSC Pos     | sitive                                 |

|      |                    | B→STN Negative, Blue                                |            | E→ISTN Ne     | gative, Black                          |

|      |                    | G→STN Positive, Gray                                |            | C→CSTN N      | egative, Black                         |

|      |                    | Y→STN Positive, Yellow                              | Green      | A→ASTN N      | egative, Black                         |

|      |                    | A: Reflective, N.T, 6:00                            |            | K: Transflee  | ctive, W.T,12:00                       |

|      | Polarizer          | D: Reflective, N.T, 12:0                            | 0          | 1: Transfled  | ctive, U.T,6:00                        |

|      | Туре,              | G: Reflective, W. T, 6:00                           | 0          | 4 : Transfleo | tive, U.T.12:00                        |

|      | Tomporaturo        | J: Reflective, W. T, 12:0                           | 0          | C : Transmis  | ssive, N.T,6:00                        |

| 6    | Temperature range, | 0 : Reflective, U. T, 6:00                          |            | F : Transmis  | sive, N.T,12:00                        |

|      | range,             | 3 : Reflective, U. T, 12:0                          | 0          | I: Transmiss  | sive, W. T, 6:00                       |

|      | View               | B: Transflective, N.T,6:0                           | 00         | L : Transmis  | sive, W.T,12:00                        |

|      | direction          | E : Transflective, N.T.12                           | :00        | 2 : Transmis  | sive, U. T, 6:00                       |

|      |                    | H: Transflective, W.T,6:                            | 00         | 5 : Transmis  | sive, U.T,12:00                        |

|      | 4                  | $N \rightarrow Without backlight$                   | W→LE       | D, White      | $H \rightarrow LED$ , High light White |

|      | 4                  | $P \rightarrow EL$ , Blue                           | A→LED      | , Amber       | S $\rightarrow$ LED, Full color        |

|      |                    | T→EL, Green                                         | R→LED      | , Red         | $J \rightarrow DIP LED, Blue$          |

| 7    | Backlight          | $D \rightarrow EL$ , White                          | O→LED      | ), Orange     | $K \rightarrow DIP LED, White$         |

|      | Buokiight          | M→EL, Yellow Green                                  | B→LED      | , Blue        | $E \rightarrow DIP LED$ , Yellow       |

|      |                    | $F \rightarrow CCFL$ , White                        | X→LED      | , Dual color  | $L \rightarrow DIP LED$ , Amber        |

|      |                    | Y→LED, Yellow Green                                 | C→LED      | , Full color  | $I \rightarrow DIP LED, Red$           |

|      | <b>Y</b>           | G→LED, Green                                        |            |               |                                        |

| 8    | Special code       | JW: English and Japane<br>V: Build in Negative Volt |            | ard font      |                                        |

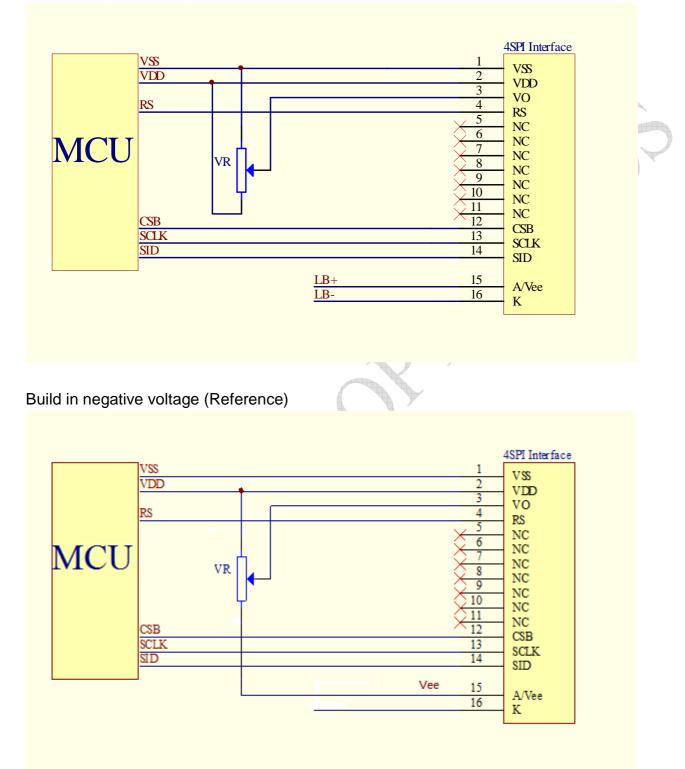

# **3.Interface Pin Function**

| Pin No. | Symbol          | Level      | Description                                                                                                                                          |

|---------|-----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>SS</sub> | 0V         | Ground                                                                                                                                               |

| 2       | $V_{DD}$        | 5.0V       | Supply Voltage for logic                                                                                                                             |

| 3       | VO              | (Variable) | Operating voltage for LCD                                                                                                                            |

| 4       | RS              | _          | In bus mode, used as register selection input.<br>When RS = "High", Date register is selected.<br>When RS = "Low", Instruction register is selected. |

| 5       | NC              | —          | No connection                                                                                                                                        |

| 6       | NC              |            | No connection                                                                                                                                        |

| 7       | NC              | —          | No connection                                                                                                                                        |

| 8       | NC              | —          | No connection                                                                                                                                        |

| 9       | NC              | _          | No connection                                                                                                                                        |

| 10      | NC              | _          | No connection                                                                                                                                        |

| 11      | NC              |            | No connection                                                                                                                                        |

| 12      | CSB             | H/L        | In 4-SPI serial mode, used as chip selection input.<br>When CSB = "Low", selected<br>When CSB = "High", not selected.<br>( Low access enable )       |

| 13      | SCLK            | H/L        | Serial clock input                                                                                                                                   |

| 14      | SID             | H/L        | Serial data input                                                                                                                                    |

| 15      | Vee             | _          | Negative Voltage Output                                                                                                                              |

| 16      | К               |            | LED-                                                                                                                                                 |

### 4.Contour Drawing &Block Diagram

| Character located | -  | -  | -  | •  | •  | ~  | •  | ~  |    |    |    |    |    | ÷ · |    | -0 |

|-------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|

| DDRAM address     |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |

| DDRAM address     | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D  | 4E | 4F |

### **5.Character Generator ROM Pattern**

Table.2

| b7∾4<br>b3∾0 | 0000              | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 10 <b>11</b> | 1100 | 110 <b>1</b> | 1110 | 1111 |

|--------------|-------------------|------|------|------|------|------|------|------|------|------|------|--------------|------|--------------|------|------|

| 0000         | CG<br>RAM<br>[00] |      |      | 8    |      |      |      |      |      |      |      |              |      |              | 8    |      |

| 0001         | сс<br>кам<br>[01] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 0010         | сс<br>кам<br>[02] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 011          | сс<br>кам<br>[03] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 0100         | CG<br>RAM<br>[04] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 0101         | CG<br>RAM<br>[05] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 0110         | CG<br>RAM<br>[06] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 0111         | CG<br>RAM<br>[07] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1000         | CG<br>RAM<br>[00] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 100 1        | Сб<br>RAM<br>[01] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1010         | сс<br>RAM<br>[02] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1011         | CG<br>RAM<br>[03] |      |      |      | K    |      |      |      |      |      |      |              |      |              |      |      |

| 1100         | CG<br>RAM<br>[04] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1101         | CG<br>RAM<br>[05] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1110         | CG<br>RAM<br>[06] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

| 1111         | CG<br>RAM<br>[07] |      |      |      |      |      |      |      |      |      |      |              |      |              |      |      |

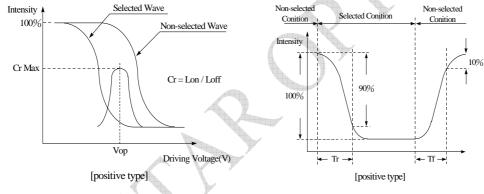

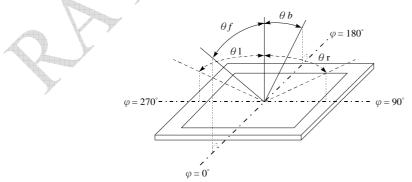

### **6.Optical Characteristics**

| ltem           | Symbol | Condition | Min           | Тур | Мах    | Unit    |

|----------------|--------|-----------|---------------|-----|--------|---------|

|                | θ      | CR≧10     | _             | 60  | _      | ψ= 180° |

|                | θ      | CR≧10     | _             | 25  | _      | ψ= 0°   |

| View Angle     | θ      | CR≧10     | _             | 40  | - (    | ψ= 90°  |

|                | θ      | CR≧10     |               | 40  | $\sim$ | ψ= 270° |

| Contrast Ratio | CR     | _         | 10            | K   |        | _       |

| Deenenee Time  | T rise | _         | _             | 300 | 350    | ms      |

| Response Time  | T fall | _         | $\mathcal{R}$ | 300 | 350    | ms      |

Definition of Operation Voltage (Vop)

Definition of Response Time (Tr, Tf)

**Conditions :**

Operating Voltage : Vop Viewin

$\label{eq:Viewing Angle} \text{Viewing Angle}(\theta \ , \ \phi) \ : \ 0^\circ \ , \ \ 0^\circ$

Frame Frequency : 64 HZ Driving Waveform : 1/N duty , 1/a bias

#### Definition of viewing angle(CR $\geq$ 2)

# 7.Absolute Maximum Ratings

| ltem                     | Symbol                          | Min                  | Тур | Max                  | Unit |

|--------------------------|---------------------------------|----------------------|-----|----------------------|------|

| Operating Temperature    | T <sub>OP</sub>                 | -20                  | _   | +70                  | °C   |

| Storage Temperature      | T <sub>ST</sub>                 | -30                  |     | +80                  | °C   |

| Input Voltage            | V <sub>IN</sub>                 | -0.3                 | _   | V <sub>DD</sub> +0.3 | V    |

| Supply Voltage For Logic | Vdd-V <sub>SS</sub>             | -0.3                 |     | 5.5                  | V    |

| Supply Voltage For LCD   | V <sub>DD</sub> -V <sub>0</sub> | V <sub>SS</sub> -0.3 | K   | V <sub>SS</sub> +7.0 | V    |

### **8.Electrical Characteristics**

| Item                     | Symbol              | Condition             | Min  | Тур | Мах                     | Unit |

|--------------------------|---------------------|-----------------------|------|-----|-------------------------|------|

| Supply Voltage For Logic | $V_{DD}$ - $V_{SS}$ |                       | 4.5  | 5.0 | 5.5                     | V    |

| Supply Voltage For LCD   |                     | <b>Ta=-20</b> ℃       | _    | _   | _                       | V    |

| *Note                    | $V_{DD}$ - $V_0$    | <b>Ta=25</b> ℃        | 6.2  | 6.5 | 6.8                     | V    |

|                          |                     | <b>Ta=70</b> ℃        | _    | _ , | $\langle \cdot \rangle$ | V    |

| Input High Volt.         | V <sub>IH</sub>     | _                     | 2.5  | ~   | V <sub>DD</sub>         | V    |

| Input Low Volt.          | V <sub>IL</sub>     | _                     | -0.3 | (-) | 0.6                     | V    |

| Output High Volt.        | V <sub>OH</sub>     | -                     | 3.9  | -   |                         | V    |

| Output Low Volt.         | V <sub>OL</sub>     | -                     | ->   | _   | 0.4                     | V    |

| Supply Current           | I <sub>DD</sub>     | V <sub>DD</sub> =5.0V | 1.0  | 1.2 | 1.5                     | mA   |

\* Note: Please design the VOP adjustment circuit on customer's main board

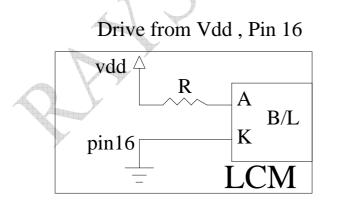

### 9.Backlight Information

#### Specification

| PARAMETER       | SYMBOL    | MIN      | ТҮР  | МАХ | UNIT              | TEST CONDITION |

|-----------------|-----------|----------|------|-----|-------------------|----------------|

| Supply Current  | ILED      | 48       | 60   | 72  | mA                | V=5.0V         |

| Supply Voltage  | V         | 4.9      | 5.0  | 5.1 | v                 | -              |

| Reverse Voltage | VR        | _        | _    | 5   | v                 | -              |

| Luminance       | IV        | 1440     | 1800 |     | CD/M <sup>2</sup> | ILED=60mA      |

| (Without LCD)   | IV        | 1440     | 1000 |     |                   |                |

| LED Life Time   |           |          |      |     | N.                | ILED=60mA      |

| (For Reference  | _         | _        | 50K  |     | Hr.               | 25℃,50-60%RH,  |

| only)           |           |          |      | K   | J.                | (Note 1)       |

| Color           | White(hig | h light) |      |     |                   |                |

Note: The LED of B/L is drive by current only, drive voltage is for reference only. drive voltage can make driving current under safety area (current between minimum and maximum).

Note 1:50K hours is only an estimate for reference.

### **10.Reliability**

#### Content of Reliability Test (Wide temperature, -20℃~70℃)

|                                       | Environmental Test                                                                                                                                                                         |                                                                                                                                                    |                                                                                                                 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Test Item                             | Content of Test                                                                                                                                                                            | Test Condition                                                                                                                                     | Note                                                                                                            |

| High Temperature<br>storage           | Endurance test applying the high storage temperature for a long time.                                                                                                                      | 200hrs 🗼                                                                                                                                           | 2                                                                                                               |

| Low Temperature<br>storage            | Endurance test applying the low storage temperature for a long time.                                                                                                                       | -30℃<br>200hrs                                                                                                                                     | 1,2                                                                                                             |

| High Temperature<br>Operation         | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.                                                                     | 70℃<br>200hrs                                                                                                                                      | Contraction of the second s |

| Low Temperature<br>Operation          | Endurance test applying the electric stress under low temperature for a long time.                                                                                                         | -20℃<br>200hrs                                                                                                                                     | 1                                                                                                               |

| High Temperature/<br>Humidity storage | The module should be allowed to stand at $60^{\circ}C$ ,90%RH max<br>For 96hrs under no-load condition excluding the polarizer,<br>Then taking it out and drying it at normal temperature. | 60°C ,90%RH<br>96hrs                                                                                                                               | 1,2                                                                                                             |

| Thermal shock<br>resistance           | The sample should be allowed stand the following 10 cycles of operation<br>-20°C 25°C 70°C<br>30 <sup>min</sup> Fmin 20 <sup>min</sup>                                                     | -20℃/70℃<br>10 cycles                                                                                                                              |                                                                                                                 |

| Vibration test                        | Endurance test applying the vibration during transportation and using.                                                                                                                     | Total fixed amplitude :<br>1.5mm<br>Vibration Frequency :<br>10~55Hz<br>One cycle 60<br>seconds to 3<br>directions of X,Y,Z for<br>Each 15 minutes | 3                                                                                                               |

| Static electricity test               | Endurance test applying the electric stress to the terminal.                                                                                                                               | VS=800V,RS=1.5kΩ<br>CS=100pF<br>1 time                                                                                                             |                                                                                                                 |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal

Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

# **11.Inspection specification**

| NO | Item                                                                  | Criterion                                                                                                  |                                                                                                                                                                                                                            |                                                                                                       |                                                                                                               |     |  |  |  |  |

|----|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

|    |                                                                       | defect.<br>1.2 Missing chara                                                                               | 1.2 Missing character , dot or icon.                                                                                                                                                                                       |                                                                                                       |                                                                                                               |     |  |  |  |  |

| 01 | Electrical<br>Testing                                                 | 1.5 Current consu<br>1.6 LCD viewing a<br>1.7 Mixed produc                                                 | <ul> <li>1.4 No function or no display.</li> <li>1.5 Current consumption exceeds product specifications.</li> <li>1.6 LCD viewing angle defect.</li> <li>1.7 Mixed product types.</li> <li>1.8 Contrast defect.</li> </ul> |                                                                                                       |                                                                                                               |     |  |  |  |  |

| 02 | Black or white<br>spots on LCD<br>(display only)                      | three white or                                                                                             | <ul> <li>2.1 White and black spots on display ≤0.25mm, no more than three white or black spots present.</li> <li>2.2 Densely spaced: No more than two spots or lines within 3mm</li> </ul>                                 |                                                                                                       |                                                                                                               |     |  |  |  |  |

| 03 | LCD black<br>spots, white<br>spots,<br>contamination<br>(non-display) | 3.1 Round type : $A$<br>$\Phi = (x + y)/2$<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A                         | Y                                                                                                                                                                                                                          | SIZE $\Phi \le 0.10$ $0.10 < \Phi \le 0.20$ $0.20 < \Phi \le 0.25$ $0.25 < \Phi$                      | Acceptable Q TY<br>Accept no dense<br>2<br>1<br>0<br>Acceptable Q TY<br>Accept no dense<br>2<br>As round type | 2.5 |  |  |  |  |

| 04 | Polarizer<br>bubbles                                                  | If bubbles are visi<br>judge using black<br>specifications, no<br>to find, must chec<br>specify direction. | spot<br>t easy                                                                                                                                                                                                             | Size $\Phi$ $\Phi \leq 0.20$ $0.20 < \Phi \leq 0.50$ $0.50 < \Phi \leq 1.00$ $1.00 < \Phi$ Total Q TY | Acceptable Q TY<br>Accept no dense<br>3<br>2<br>0<br>3                                                        | 2.5 |  |  |  |  |

| NO                | Item       |                                                         | Criterion                    |                   | AQL           |  |  |  |  |

|-------------------|------------|---------------------------------------------------------|------------------------------|-------------------|---------------|--|--|--|--|

| 05                | Scratches  | Follow NO.3 LCD black spots, white spots, contamination |                              |                   |               |  |  |  |  |

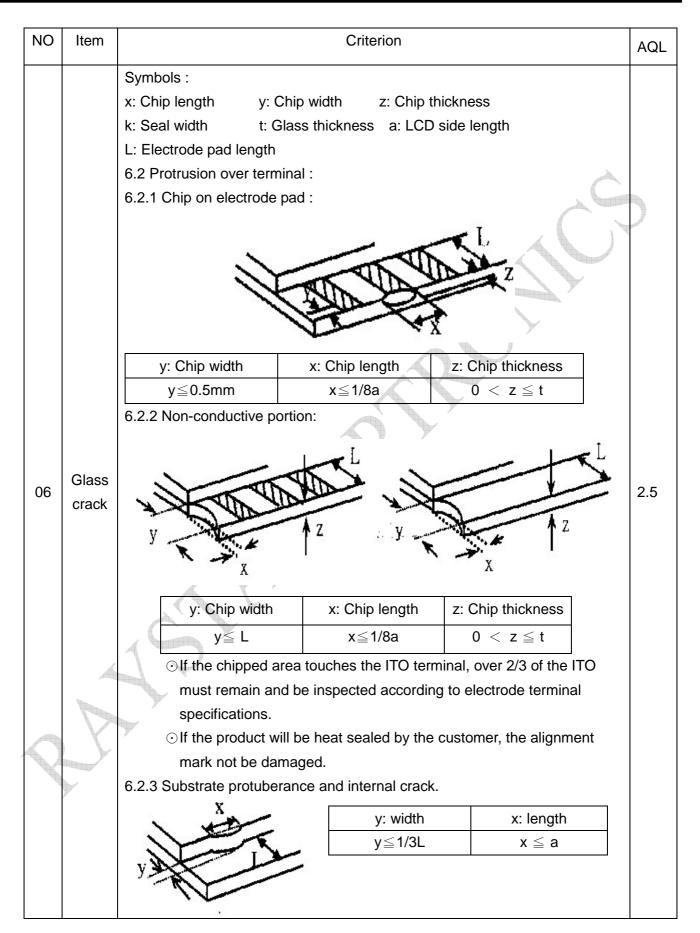

|                   |            | Symbols Define:                                         |                              |                   |               |  |  |  |  |

|                   |            | x: Chip length y:                                       | Chip width z: Chip           | thickness         |               |  |  |  |  |

|                   |            | k: Seal width t: 0                                      | Glass thickness a: LCE       | D side length     |               |  |  |  |  |

|                   |            | L: Electrode pad length                                 | :                            |                   |               |  |  |  |  |

|                   |            |                                                         |                              | , C               |               |  |  |  |  |

|                   |            | 6.1 General glass chip                                  |                              |                   | $\mathcal{D}$ |  |  |  |  |

|                   |            | 6.1.1 Chip on panel su                                  | rface and crack between      | panels:           | <i>K</i>      |  |  |  |  |

|                   |            | ×                                                       |                              | 2 V               |               |  |  |  |  |

|                   |            | z: Chip thickness                                       | y: Chip width                | x: Chip length    |               |  |  |  |  |

|                   |            | Z≦1/2t                                                  | Not over viewing             | x≦1/8a            |               |  |  |  |  |

| 06                | Chipped    |                                                         | area                         |                   | 2.5           |  |  |  |  |

|                   | glass      | $1/2t < z \leq 2t$                                      | Not exceed 1/3k              | x≦1/8a            |               |  |  |  |  |

|                   |            | $\odot$ If there are 2 or more                          | chips, x is total length o   | of each chip.     |               |  |  |  |  |

|                   |            |                                                         |                              |                   |               |  |  |  |  |

|                   |            | 6.1.2 Corner crack:                                     |                              |                   |               |  |  |  |  |

|                   |            |                                                         | 17 1                         | v                 |               |  |  |  |  |

|                   | , (        |                                                         | X X X                        | У                 |               |  |  |  |  |

|                   |            |                                                         | VET                          |                   |               |  |  |  |  |

|                   | AN         |                                                         | VE                           |                   |               |  |  |  |  |

|                   |            | 7                                                       |                              |                   |               |  |  |  |  |

|                   |            | <br>                                                    | 1                            |                   |               |  |  |  |  |

| $\langle \rangle$ |            | z: Chip thickness                                       | y: Chip width                | x: Chip length    |               |  |  |  |  |

|                   |            | Z≦1/2t                                                  | Not over viewing             | x≦1/8a            |               |  |  |  |  |

|                   | <i>I</i> 7 |                                                         | area                         |                   |               |  |  |  |  |

|                   |            | $1/2t < z \leq 2t$                                      | Not exceed 1/3k              | x≦1/8a            |               |  |  |  |  |

|                   |            | $\odot$ If there are 2 or more                          | e chips, x is the total leng | oth of each chip. |               |  |  |  |  |

|                   |            |                                                         |                              |                   |               |  |  |  |  |

RAYSTAR

| NO | Item          | Criterion                                                                                                         | AQL    |

|----|---------------|-------------------------------------------------------------------------------------------------------------------|--------|

| 07 | Cracked glass | The LCD with extensive crack is not acceptable.                                                                   | 2.5    |

|    |               | 8.1 Illumination source flickers when lit.                                                                        | 0.65   |

| 08 | Backlight     | 8.2 Spots or scratched that appear when lit must be judged.                                                       | 2.5    |

|    | elements      | Using LCD spot, lines and contamination standards.                                                                | $\sim$ |

|    |               | 8.3 Backlight doesn't light or color wrong.                                                                       | 0.65   |

|    |               | 9.1 Bezel may not have rust, be deformed or have fingerprints,                                                    | 2.5    |

| 09 | Bezel         | stains or other contamination.                                                                                    | 0.65   |

|    |               | 9.2 Bezel must comply with job specifications.                                                                    |        |

|    |               | 10.1 COB seal may not have pinholes larger than 0.2mm or                                                          |        |

|    |               | contamination.                                                                                                    | 2.5    |

|    |               | 10.2 COB seal surface may not have pinholes through to the IC.                                                    |        |

|    |               | 10.3 The height of the COB should not exceed the height                                                           | 2.5    |

|    |               | indicated in the assembly diagram.                                                                                | 0.65   |

|    |               | 10.4 There may not be more than 2mm of sealant outside the seal area on the PCB. And there should be no more than |        |

|    |               | three places.                                                                                                     | 2.5    |

|    |               | 10.5 No oxidation or contamination PCB terminals.                                                                 |        |

| 10 |               | 10.6 Parts on PCB must be the same as on the production                                                           | 2.5    |

| 10 |               | characteristic chart. There should be no wrong parts,                                                             | 0.65   |

|    |               | missing parts or excess parts.                                                                                    | 0.00   |

|    |               | 10.7 The jumper on the PCB should conform to the product                                                          |        |

|    | , C           | characteristic chart.                                                                                             | 0.65   |

|    |               | 10.8 If solder gets on bezel tab pads, LED pad, zebra pad or                                                      | 0.00   |

|    |               | screw hold pad, make sure it is smoothed down.                                                                    | 2.5    |

|    | Y Y           | 10.9 The Scraping testing standard for Copper Coating of PCB                                                      |        |

|    |               | X                                                                                                                 | 2.5    |

| N  |               | Y X * Y<=2mm2                                                                                                     |        |

|    | Y             | 11.1 No un-melted solder paste may be present on the PCB.                                                         | 2.5    |

|    |               | 11.2 No cold solder joints, missing solder connections, oxidation                                                 | 2.5    |

| 11 | Soldering     | or icicle.                                                                                                        |        |

|    | Coldonnig     | 11.3 No residue or solder balls on PCB.                                                                           | 2.5    |

|    |               | 11.4 No short circuits in components on PCB.                                                                      | 0.65   |

|    |               |                                                                                                                   | 0.00   |

| NO | Item       | Criterion                                                                            | AQL  |

|----|------------|--------------------------------------------------------------------------------------|------|

|    |            | 12.1 No oxidation, contamination, curves or, bends on interface<br>Pin (OLB) of TCP. | 2.5  |

|    |            | 12.2 No cracks on interface pin (OLB) of TCP.                                        | 0.65 |

|    |            | 12.3 No contamination, solder residue or solder balls on product.                    | 2.5  |

|    |            | 12.4 The IC on the TCP may not be damaged, circuits.                                 | 2.5  |

|    | General    | 12.5 The uppermost edge of the protective strip on the interface                     | 2.5  |

|    |            | pin must be present or look as if it cause the interface pin to                      |      |

|    |            | sever.                                                                               | 2.5  |

| 12 | appearance | 12.6 The residual rosin or tin oil of soldering (component or chip                   |      |

|    |            | component) is not burned into brown or black color.                                  | 2.5  |

|    |            | 12.7 Sealant on top of the ITO circuit has not hardened.                             | 0.65 |

|    |            | 12.8 Pin type must match type in specification sheet.                                | 0.65 |

|    |            | 12.9 LCD pin loose or missing pins.                                                  | 0.65 |

|    |            | 12.10 Product packaging must the same as specified on                                |      |

|    |            | packaging specification sheet.                                                       | 0.65 |

|    |            | 12.11 Product dimension and structure must conform to product specification sheet.   |      |

|    |            | 12.12 Visual defect outside of VA is not considered to be rejection.                 |      |

### **12.Precautions in use of LCD Modules**

- (1)Avoid applying excessive shocks to the module or making any alterations or modifications to it.

- (2)Don't make extra holes on the printed circuit board, modify its shape or change the components of LCD module.

- (3)Don't disassemble the LCM.

- (4)Don't operate it above the absolute maximum rating.

- (5)Don't drop, bend or twist LCM.

- (6)Soldering: only to the I/O terminals.

- (7)Storage: please storage in anti-static electricity container and clean environment.

- (8) Raystar have the right to change the passive components, including R3,R6 & backlight adjust resistors. (Resistors,capacitors and other passive components will have different appearance and color caused by the different supplier.)

- (9)Raystar have the right to change the PCB Rev. (In order to satisfy the supplying stability, management optimization and the best product performance...etc, under the premise of not affecting the electrical characteristics and external dimensions, Raystar have the right to modify the version.)

### **13.Material List of Components for RoHs**

1. RAYSTAR Display Co., Ltd hereby declares that all of or part of products (with the mark "#"in code), including, but not limited to, the LCM, accessories or packages, manufactured and/or delivered to your company (including your subsidiaries and affiliated company) directly or indirectly by our company (including our subsidiaries or affiliated companies) do not intentionally contain any of the substances listed in all applicable EU directives and regulations, including the following substances.

Exhibit A : The Harmful Material List

| Material    | (Cd)                                             | (Pb) | (Hg) | (Cr6+) | PBBs | PBDEs |  |  |  |  |  |

|-------------|--------------------------------------------------|------|------|--------|------|-------|--|--|--|--|--|

| Limited     | 100                                              | 1000 | 1000 | 1000   | 1000 | 1000  |  |  |  |  |  |

| Value       | ppm                                              | ppm  | ppm  | ppm    | ppm  | ppm   |  |  |  |  |  |

| Above limit | Above limited value is set up according to RoHS. |      |      |        |      |       |  |  |  |  |  |

- 2.Process for RoHS requirement :

- (1) Use the Sn/Ag/Cu soldering surface ; the surface of Pb-free solder is rougher than we used before.

- (2) Heat-resistance temp. :

Reflow : 250°C, 30 seconds Max. ;

Connector soldering wave or hand soldering :  $320^{\circ}$ C, 10 seconds max.

(3) Temp. curve of reflow, max. Temp. :  $235\pm5^{\circ}$ C ;

Recommended customer's soldering temp. of connector :  $280^{\circ}$ C, 3 seconds.

### 14. Recommendable Storage

- 1. Place the panel or module in the temperature 25°C±5°C and the humidity below 65% RH

- 2. Do not place the module near organics solvents or corrosive gases.

- 3. Do not crush, shake, or jolt the module.

Page: 1

|                                       | LCM Sample     | e Estimate Feedback Sheet |

|---------------------------------------|----------------|---------------------------|

| Module Number :                       |                |                           |

| 1 · Panel Specification :             |                |                           |

| 1. Panel Type :                       | Pass           | □ NG ,                    |

| 2. View Direction :                   | Pass           | □ NG ,                    |

| 3. Numbers of Dots :                  | Pass           | □ NG ,                    |

| 4. View Area :                        | Pass           | □ NG ,                    |

| 5. Active Area :                      | Pass           | □ NG ,                    |

| 6.Operating Temperature :             | Pass           | □ NG ,                    |

| 7.Storage Temperature :               | Pass           | □ NG ,                    |

| 8.Others :                            |                |                           |

| 2 · <u>Mechanical Specification</u> : |                |                           |

| 1. PCB Size :                         | Pass           | □ NG ,                    |

| 2.Frame Size :                        | Pass           | □ NG ,                    |

| 3.Materal of Frame :                  | Pass           | □ NG ,                    |

| 4.Connector Position :                | Pass           | □ NG ,                    |

| 5.Fix Hole Position :                 | Pass           | □ NG ,                    |

| 6.Backlight Position :                | Pass           | □ NG ,                    |

| 7. Thickness of PCB :                 | Pass           | □ NG ,                    |

| 8. Height of Frame to PCB :           | 🗆 Pass         | □ NG ,                    |

| 9.Height of Module :                  |                | □ NG ,                    |

| 10.Others :                           | Pass           | □ NG ,                    |

| 3 · <u>Relative Hole Size</u> :       |                |                           |

| 1.Pitch of Connector :                | Pass           | □ NG ,                    |

| 2.Hole size of Connector :            | Pass           | □ NG ,                    |

| 3.Mounting Hole size :                | Pass           | □ NG ,                    |

| 4.Mounting Hole Type :                | Pass           | □ NG ,                    |

| 5.Others :                            | Pass           | □ NG ,                    |

| 4 · Backlight Specification :         |                |                           |

| 1.B/L Type:                           | Pass           | □ NG ,                    |

| 2.B/L Color :                         | Pass           | □ NG ,                    |

| 3.B/L Driving Voltage (Referer        | nce for LED Ty | /pe):□ Pass □ NG ,        |

| 4.B/L Driving Current :               | Pass           | □ NG ,                    |

| 5.Brightness of B/L :                 | Pass           | □ NG ,                    |

| 6.B/L Solder Method :                 | Pass           | □ NG ,                    |

| 7.Others :                            | Pass           | □ NG ,                    |

>> Go to page 2 <<

Page: 2

| Module Number :                   |             | Fay    |

|-----------------------------------|-------------|--------|

| 5 · Electronic Characteristics of | of Module : |        |

| 1.Input Voltage :                 | □ Pass      | □ NG , |

| 2.Supply Current :                | Pass        | □ NG , |

| 3.Driving Voltage for LCD :       | Pass        | □ NG , |

| 4.Contrast for LCD :              | Pass        | □ NG , |

| 5.B/L Driving Method :            | Pass        | □ NG , |

| 6.Negative Voltage Output :       | Pass        | □ NG , |

| 7.Interface Function :            | □ Pass      | □ NG , |

| 8.LCD Uniformity :                | Pass        | □ NG , |

| 9.ESD test :                      | Pass        | □ NG , |

| 10.Others :                       | Pass        | □ NG , |

| 6                                 |             |        |

Sales signature : \_\_\_\_\_ Customer Signature : \_\_\_\_\_

| Date | : | 1 | 1 |   |

|------|---|---|---|---|

|      |   |   |   | _ |

### **15.Other (IC Information)**

### **1.Function Description**

#### SYSTEM INTERFACE (Parallel 8-bit bus and 4-bit bus)

This chip has all four kinds interface type with MPU: IIC, 4SPI, 4-bit bus and 8-bit bus. Serial and parallel buses (4-bit/8-bit) are selected by IF1 and IF0 input pins, and 4-bit bus and 8-bit bus is selected by DL bit in the instruction register.

During read or write operation, two 8-bit registers are used. One is data register (DR); the other is instruction register (IR). The data register (DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM, target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. So to speak, after MPU reads DR data, the data in the next DDRAM/CGRAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM automatically.

The Instruction register (IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

IR: Instruction Register.

DR: Data Register.

| RS | R/W | Operation                                                         |

|----|-----|-------------------------------------------------------------------|

| 0  | 0   | Instruction write operation (MPU writes Instruction code into IR) |

| 0  | 1   | Read busy flag (DB7) and address counter (DB0 - DB6)              |

| 1  | 0   | Data write operation (MPU writes data into DR                     |

| 1  | 1   | Data read operation (MPU reads data from DR)                      |

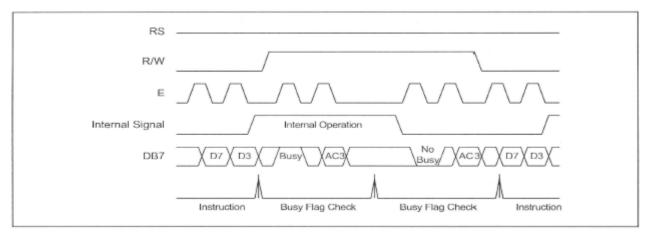

#### BUSY FLAG (BF) (only support parallel 8-bit bus and 4-bit bus)

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS = Low and R / W = High (Read Instruction Operation); through DB7 before executing the next instruction, be sure that BF is not High.

#### **DISPLAY DATA RAM (DDRAM)**

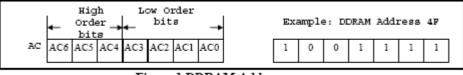

DDRAM stores display data of maximum 80 x 8 bits (80 characters). DDRAM address is set in the address counter (AC) as a hexadecimal number. (Refer to Figure 1.)

Figure 1 DDRAM Address

Since DDRAM has 8 bits data. It is possible to access 256 CGROM/CGRAM fonts.

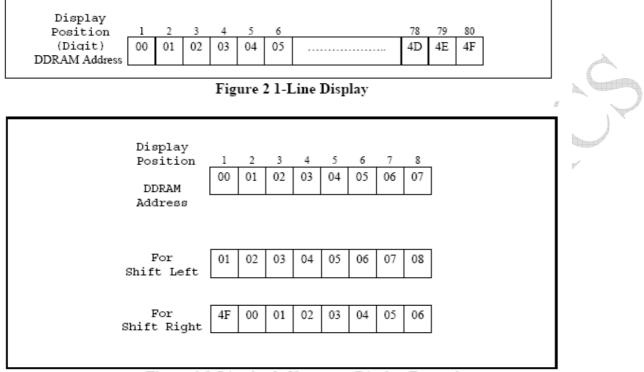

#### 1-line display (N = 0) (Figure 2)

When there are fewer than 80 display characters, the display begins at the head position. For example, if using only the Controller, 8 characters are displayed. See Figure 3.

When the display shift operation is performed, the DDRAM address shifts. See Figure 3.

Figure 3 1-Line by 8-Character Display Example

#### 2-line display (N = 1) (Figure 4)

Case 1: When the number of display characters is less than 40 x 2 lines, the two lines are displayed from the head. Note that the first line end address and the second line start address are not consecutive. For example, when just the Controller is used, 8 characters x 2 lines are displayed. See Figure 5.

When display shift operation is performed, the DDRAM address shifts. See Figure 5.

| Display<br>Position      | 1  | 2  | 3  | 4  | 5  | 6  | 38     | 39 | 40 |

|--------------------------|----|----|----|----|----|----|--------|----|----|

| DDRAM                    | 00 | 01 | 02 | 03 | 04 | 05 | <br>25 | 26 | 27 |

| Address<br>(hexadecimal) | 40 | 41 | 42 | 43 | 44 | 45 | <br>65 | 66 | 67 |

Figure 4 2-Lines Display

Figure 5 2-Lines by 8-Character Display Example

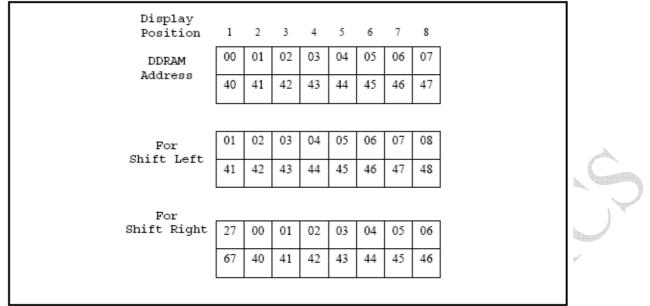

Case 2: For a 16-character x 2-line display, the Controller can be extended using one 40-output extension driver. See Figure 6.

When display shift operation is performed, the DDRAM address shifts. See Figure 6.

| Display           | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |  |

|-------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--|

| Position<br>DDRAM | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |  |

| Address           | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |  |

|                   |    | ·  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

| For<br>Shift      | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 |  |

| Left              | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 |  |

|                   |    |    |    | ·  |    |    |    |    |    |    |    |    |    |    |    |    |  |

| For<br>Shift      | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E |  |

| Right             | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E |  |

|                   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

| Figure | 6 2-] | Lines | bv | 16-Character | Display | Example |

|--------|-------|-------|----|--------------|---------|---------|

|        |       |       |    |              |         |         |

y

#### TIMING GENERATION CIRCUIT

Timing generation circuit generates clock signals for the internal operations.

#### ADDRESS COUNTER (AC)

Address Counter (AC) stores DDRAM/CGRAM address, transferred from IR.

After writing into (reading from) DDRAM/CGRAM/SEGRAM, AC is automatically increased (decreased) by 1.

When RS = "Low" and R/W = "High", AC can be read through DB0-DB6

#### CURSOR/BLINK CONTROL CIRCUIT

It controls cursor/blink ON/OFF and black/white inversion at cursor position.

#### LCD DRIVER CIRCUIT

LCD Driver circuit has 16 common and 40 segment signals for 2-line display (N=1) or 8 common and 40 segments for 1-line display (N=0) for LCD driving.

Data from CGRAM/CGROM is transferred to 40 bit segment latches serially, and then it is stored to 40 bit shift latch.

#### **CGROM (CHARACTER GENERATOR ROM)**

CGROM has 10,240 bits (256 characters x 5 x 8 dot)

#### **CGRAM (CHARACTER GENERATOR RAM)**

CGRAM has up to 5 8 dots 8 characters. By writing font data to CGRAM, user defined character can be used (refer to Table 2).

#### 5 x 8 dots Character Pattern

#### Table 2. Relationship between Character Code (DDRAM) and Character Pattern (CGRAM)

| Pattern   |    |    | ata | M D | GRA | - C |    |    |    | ress | I Add | RAN | CG |    | )  | f data | RAM | (DD | Code | acter | Char |    |

|-----------|----|----|-----|-----|-----|-----|----|----|----|------|-------|-----|----|----|----|--------|-----|-----|------|-------|------|----|

| Number    | PO | P1 | P2  | P3  | P4  | P5  | P6 | P7 | A0 | Α1   | A2    | A3  | A4 | A5 | D0 | D1     | D2  | D3  | D4   | D5    | D6   | D7 |

| Pattern 1 | 0  | 1  | 1   | 1   | 0   | Х   | Х  | Х  | 0  | 0    | 0     | 0   | 0  | 0  | 0  | 0      | 0   | 0   | 0    | 0     | 0    | 0  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 1  | 0    | 0     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 0  | 1    | 0     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 1  | 1  | 1   | 1   | 1   | -   | -  | -  | 1  | 1    | 0     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 0  | 0    | 1     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 1  | 0    | 1     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 0  | 1    | 1     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           | 0  | 0  | 0   | 0   | 0   | -   | -  | -  | 1  | 1    | 1     | -   | -  | -  | 0  | 0      | 0   | -   | -    | -     | -    | -  |

|           |    |    |     | -   |     |     |    |    |    | -    |       |     | -  |    |    |        |     | -   |      |       |      |    |

| D         | 1  | ~  | 0   | •   | - 1 | v   | v  | v  | 0  | •    | 0     | 1   | -  | 1  | 1  | 1      | 1   | •   | 0    | 0     | 0    | 0  |

| Pattern 8 | 1  | 0  | 0   | 0   | 1   | Х   | Х  | Х  | 0  | 0    | 0     | 1   | 1  | 1  | 1  | 1      | 1   | 0   | 0    | 0     | 0    | 0  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 1  | 0    | 0     | -   | -  | -  | 1  | 1      | 1   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 1   | 0   | 1   | -   | -  | -  | 0  | 1    | 0     | -   | -  | -  | 1  | 1      | 1   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   | -   | -  | -  | 0  | 0    | 1     | -   | -  | -  | 1  | 1      | 1   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | 0   | 1   |     |    |    | 1  | 0    | 1     |     | -  |    | 1  | 1      | 1   | -   | -    | -     | -    | -  |

|           | 1  | 0  | 0   | ŏ   | 1   |     |    |    | 0  | 1    | 1     |     | -  |    | 1  | 1      | 1   | -   | -    | -     | -    |    |

|           | 0  | 0  | 0   | 0   | 0   |     |    |    | 1  | 1    | 1     | -   | -  |    | 1  | 1      | 1   |     | -    | -     | _    |    |

|           | -0 | v  | 0   | v   | 0   |     |    |    | T  | 1    | 1     |     |    |    | 1  | 1      | 1   |     |      |       |      |    |

Notes:

1. Character code bits 0 to 2 correspond to CGRAM address bits 3 to 5 (3 bits: 8 types).

2. CGRAM address bits 0 to 2 designate the character pattern line position. The 8th line is the cursor position and its display is formed by a logical OR with the cursor. Maintain the 8th line data, corresponding to the cursor display position, at 0 as the cursor display. If the 8th line data is

1, 1 bit will light up the 8th line regardless of the cursor presence.

3. Character pattern row positions correspond to CGRAM data bits 0 to 4 (bit 4 being at the left).

4. As shown Table 2, CGRAM character patterns are selected when character code bits 4 to 7 are all 0 and MW=0. However, since character code bit 3 has no effect, the H display example above can be selected by either character code 00H or 08H.

5. 1 for CGRAM data corresponds to display selection and 0 to non-selection. "-": Indicates no effect.

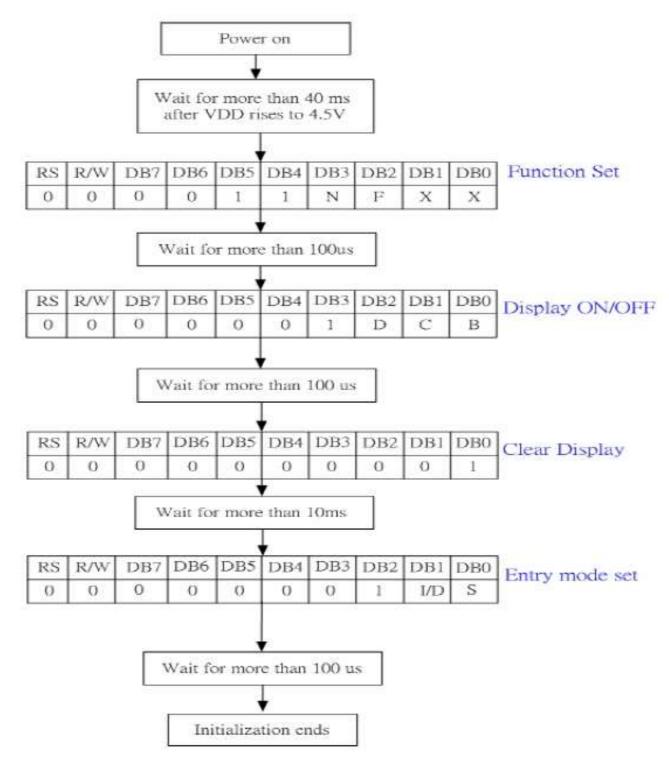

### 2.Instruction Table

| Instruction                   | RS | RW | DB7 | DB6 | DB5 | DB4   | DB3    | DB2 | DB1 | DB0 | Description                                                                                                                                                            | Description<br>Time<br>(540KHz) |

|-------------------------------|----|----|-----|-----|-----|-------|--------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Read display data             | 1  | 1  |     |     |     | Read  | l data |     |     |     | Read data into DDRAM/CGRAM/SEGRAM                                                                                                                                      | 18.5us                          |

| Write display data            | 1  | 0  |     |     |     | Write | e data |     |     |     | Write data into DDRAM/CGRAM/SEGRAM                                                                                                                                     | 18.5us                          |

| Clear Display                 | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 1   | Write "20H" to DDRAM, and set DDRAM<br>address to "00H" from AC                                                                                                        | 0.76ms                          |

| Return Home                   | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0   | 1   | Х   | Set DDRAM address to "00H" from AC and<br>return cursor to its original position if shifted.<br>The contents of DDRAM are not changed.                                 | 0.76ms                          |

| Entry Mode Set                | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 1   | I/D | S   | Assign cursor moving direction and specify<br>display shift. These operations are performed<br>during data read and write.<br>I/D="1": increment<br>I/D="0": decrement | 18.5us                          |

| Display ON/OFF                | 0  | 0  | 0   | 0   | 0   | 0     | 1      | D   | С   | В   | Set Display /Cursor/Blink On/OFF<br>D="1": display on<br>D="0": display off<br>C="1": cursor on<br>C="0": cursor off<br>B="1": blink on<br>B="0": blink off            | 18.5us                          |

| Cursor or Display shift       | 0  | 0  | 0   | 0   | 0   | 1     | S/C    | R/L | Х   | Х   | Cursor or display shift<br>S/C="1": display shift<br>S/C="0": cursor shift<br>R/L="1": shift to right<br>R/L="0": shift to left                                        | 18.5us                          |

| Function Set                  | 0  | 0  | 0   | 0   | 1   | DL    | N      | F   | Х   | Х   | Set Interface Data Length<br>DL= 8-bit interface/ 4-bit interface<br>N = 2-line/1-line display<br>F= 5x8 Font Size / 5x11Font Size                                     | 18.5us                          |

| Set CGRAM Address             | 0  | 0  | 0   | 1   | AC5 | AC4   | AC3    | AC2 | AC1 | AC0 | Set CGRAM address in address counter                                                                                                                                   | 18.5us                          |

| Set DDRAM Address             | 0  | 0  | 1   | AC6 | AC5 | AC4   | AC3    | AC2 | AC1 | AC0 | Set DDRAM address in address counter                                                                                                                                   | 18.5us                          |

| Read Busy Flag and<br>Address | 0  | 1  | BF  | AC6 | AC5 | AC4   | AC3    | AC2 | AC1 | AC0 | Can know internal operation is ready or not by<br>reading BF.<br>The contents of address counter can also be<br>read.<br>BF="1": busy state<br>BF="0": ready state     | Ous                             |

#### **Clear Display**

| <br>RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter). Return cursor to the original status; namely, bring the cursor to the left edge on first line of the display. Make entry mode increment (I/D = "1").

#### **Return Home:**

|   |   |     |     |     |     |     |     |     |     | ten |

|---|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| R | 6 | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 |   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Х   |

Return Home is cursor return home instruction. Set DDRAM address to "00H" into the address counter. Return cursor to its original site and return display to its original status, if shifted. A content of DDRAM does not change.

#### **Entry Mode Set:**

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

Set the moving direction of cursor and display.

#### I/D: Increment/decrement of DDRAM address (cursor or blink)

I/D = 1: cursor/blink moves to right and DDRAM address is increased by 1.

I/D = 0: cursor/blink moves to left and DDRAM address is decreased by 1.

\* CGRAM operates the same as DDRAM, when read/write from or to CGRAM

#### S: Shift of entire display

When DDRAM read (CGRAM read/write) operation or S = "Low", shift of entire display is not performed.

If S= "High" and DDRAM write operation, shift of entire display is performed according to I/D value (I/D = "1": shift left, I/D = "0": shift right).

| s | I/D | Description                    |

|---|-----|--------------------------------|

| Н | Н   | Shift the display to the left  |

| Н | L   | Shift the display to the right |

#### **Display ON/OFF**

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

Control display/cursor/blink ON/OFF 1 bit register.

#### D: Display ON/OFF control bit.

D = 1: entire display is turned on.

D = 0: display is turned off, but display data is remained in DDRAM.

#### C: Cursor ON/OFF control bit.

C = 1: cursor is turned on.

C = 0: cursor is disappeared in current display, but I/D register remains its data.

#### B: Cursor Blink ON/OFF control bit.

B = 1: cursor blink is on, that performs alternate between all the high data and display character at the cursor position. If fosc has 540 kHz frequency, blinking has 185 ms interval. B = 0: blink is off.

#### **Cursor or Display Shift**

|    | Display | Onne |     |     |     |     |     |     |     |

|----|---------|------|-----|-----|-----|-----|-----|-----|-----|

| RS | R/W     | DB7  | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0  | 0       | 0    | 0   | 0   | 1   | S/C | R/L | -   | -   |

Without writing or reading of display data, shift right/left cursor position or display. This instruction is used to correct or search display data (refer to Table 4). During 2-line mode display, cursor moves to the 2nd line after 40th digit of 1st line.

Note that display shift is performed simultaneously by the shift enable instruction. When displayed data is shifted repeatedly, all display lines shifted simultaneously. When display shift is performed, the contents of address counter are not changed.

#### Table 4. Shift Patterns According to S/C and R/L Bits

| S/C | R/L | Operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, address counter is decreased by 1               |

| 0   | 1   | Shift cursor to the right, address counter is increased by 1              |

| 1   | 0   | Shift all the display to the left, cursor moves according to the display  |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

#### **Function Set**

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | DL  | N   | F   | Х   | Х   |

#### DL: Interface data length control bit

When DL = "High", it means 8-bit bus mode with MPU.

When DL = "Low", it means 4-bit bus mode with MPU. So to speak, DL is a signal to select 8-bit or 4-bit bus mode.

When 4-bit bus mode, it needs to transfer 4-bit data by two times.

IF using IIC and 4-SPI interface . DL bit must be setting to "1"

#### N: Display line number control bit

When N = "Low", it means 1-line display mode.

When N = "High", 2-line display mode is set.

#### F: Display font type control bit

When F = "Low", it means 5 x 8 dots format display mode

When F = "High", 5 x11 dots format display mode.

| Ν | F | No. of Display Lines | Character Font | Duty Factor |

|---|---|----------------------|----------------|-------------|

| L | L | 1                    | 5x8            | 1/8         |

| L | Н | 1                    | 5x11           | 1/11        |

| Н | x | 2                    | 5x8            | 1/16        |

#### Set CGRAM Address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set CGRAM address to AC.

This instruction makes CGRAM data available from MPU.

| S | Set DDRAM Address |     |     |     |     |     |     |     |     |     |

|---|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | RS                | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| [ | 0                 | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

#### Set DDRAM address to AC.

This instruction makes DDRAM data available from MPU.

When 1-line display mode (N=0), DDRAM address is from "00H" to "4FH"

In 2-line display mode (NW = 0), DDRAM address in the 1st line is from "00H" - "27H", and DDRAM address in the 2nd line is from "40H" - "67H".

#### Read Busy Flag and Address (only support parallel 8-bit bus and 4 bit bus)

|   | De | R/W        | DB7 | DRC | DBE | DB4 | <b>DD</b> 2 | 002 | DD1 | DB0 |

|---|----|------------|-----|-----|-----|-----|-------------|-----|-----|-----|

| _ | КЭ | <b>K/W</b> | ופט |     | DBC | UD4 | 063         | DB2 |     | рво |

| [ | 0  | 1          | BF  | AC6 | AC5 | AC4 | AC3         | AC2 | AC1 | AC0 |

This instruction shows whether Controller is in internal operation or not. If the resultant BF is "high", it means the internal operation is in progress and you have to wait until BF to be Low, and then the next instruction can be performed. In this instruction you can read also the value of address counter.

#### Write Data to RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM/SEGRAM.

The selection of RAM from DDRAM, CGRAM, is set by the previous address set instruction: DDRAM address set, CGRAM address set. RAM set instruction can also determine the AC direction to RAM.

After write operation, the address is automatically increased/decreased by 1, according to the entry mode.

Read Data from RAM (only support parallel 8-bit bus and 4 bit bus)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If address set instruction of RAM is not performed before this instruction, the data that read first is invalid, because the direction of AC is not determined.

If you read RAM data several times without RAM address set instruction before read operation, you can get correct RAM data from the second, but the first data would be incorrect, because there is no time margin to transfer RAM data.

In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction: it also transfer RAM data to output data register. After read operation address counter is automatically increased/decreased by 1 according to the entry mode. After CGRAM read operation, display shift may not be executed correctly.

\* In case of RAM write operation, after this AC is increased/decreased by 1 like read operation. In this time, AC indicates the next address position, but you can read only the previous data by read instruction.

#### OUTLINE

To overcome the speed difference between internal clock of Controller and MPU clock,

Controller performs internal operation by storing control information to IR (Instruction Register) or DR (data Register).

The internal operation is determined according to the signal from MPU, composed of read/write and data bus.

I Nstruction can be divided largely four kinds;

\*Controller function set instructions (set display methods, set data length, etc.)

\*Address set instructions to internal RAM

\*Data transfer instructions with internal RAM

\*Others

The address of internal RAM is automatically increased or decreased by 1.

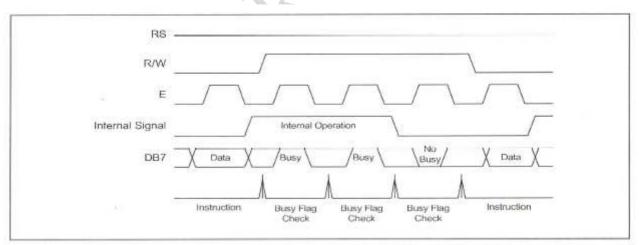

**NOTE:** During internal operation, Busy Flag (DB7) is read high. Busy Flag check must be preceded the next instruction.

Busy flag check must be proceeded the next instruction.

When an MPU program with Busy Flag (DB7) checking is made, 1/2 Fosc (is necessary) for executing the next instruction by the falling edge of the "E" signal after the Busy Flag (DB7) goes to "Low".

#### INTERFACE WITH MPU

Controller can transfer data in bus mode (4-bit or 8-bit) or serial mode with MPU.

In case of 4-bit bus mode, data transfer is performed by two times to transfer 1 byte data.

When interfacing data lengths are 4-bit, only 4 ports, from DB4 - DB7, are used as data bus. At first higher 4-bit (in case of 8-bit bus mode, the contents of DB4 - DB7) are transferred, and then lower 4- bit (in case of 8-bit bus mode, the contents of DB0 - DB3) are transferred. So transfer is performed by two times.

Busy Flag outputs "High" after the second transfer are ended.

When interfacing data length are 8-bit, transfer is performed at a time through 8 ports, from DB0 - DB7.

Interface is selected by IF1, IF0 pins (refer to **Bonding Note for IF1, IF0** on Page 10)

| IF1            | IF0            | Interface select |  |  |

|----------------|----------------|------------------|--|--|

| open           | open           | 6800 8/4 bit     |  |  |

| open           | Bonding to VDD | IIC              |  |  |

| Bonding to VDD | open           | 4-line SPI       |  |  |

#### INTERFACE WITH MPU IN BUS MODE

#### Interface with 8-bit MPU

If 8-bits MPU is used, Controller can connect directly with that. In this case, port E, RS, R/W and DB0 to DB7 need to interface each other. Example of timing sequence is shown below.

Example of 8-bit Bus Mode Timing Sequence

#### Interface with 4-bit MPU

If 4-bit MPU is used, Controller can connect directly with this. In this case, port E, RS, R/W and DB4 - DB7 need to interface each other. The transfer is performed by two times. Example of timing sequence is shown below.

Example of 4-bit Bus Mode Timing Sequence

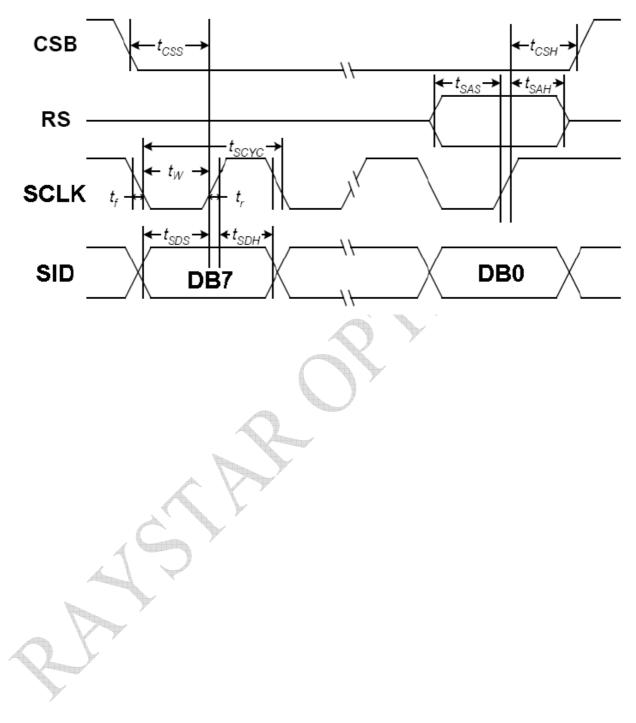

#### For serial interface data, bus lines (DB5 to DB7) are used. 4-Line SPI

If 4-Pin SPI mode is used, CSB (DB5), SID (DB7), SCLK (DB6), and RS are used. They are chip selection; serial input data, serial clock input, and data/instruction section, relatively. The example of timing sequence is shown below.

#### Example of timing sequence

| CSB  |                                                                       |

|------|-----------------------------------------------------------------------|

| SID  | D7 \ D6 \ D5 \ D4 \ D3 \ D2 \ D1 \ D0 \ D7 \ D6 \ D5 \ D4 \ D3 \ D2 \ |

| SCLK |                                                                       |

| RS   |                                                                       |

Note: Following is the master SPI clock mode of MPU.

Idle state for clock is a high level , data transmitted on rising edge of SCLK, and data is hold during low level.

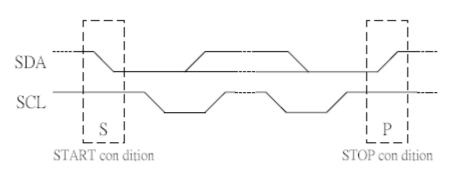

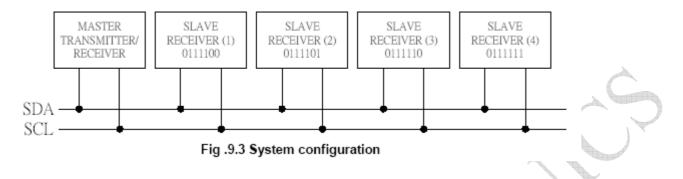

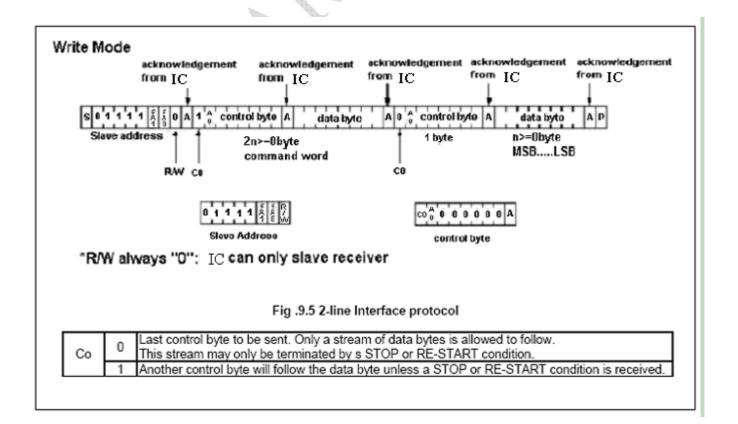

# For serial interface data, bus lines (DB5(CSB) DB6(SDA) and DB7(SCL)) are used. IIC interface

The IIC interface receives and executes the commands sent via the IIC Interface. It also receives RAM data and sends it to the RAM.

The IIC Interface is for bi-directional, two-line communication between different ICs or modules. Serial data line

SDA (DB6) and a Serial clock line SCL (DB7) must be connected to a positive supply via a pull-up resistor.

Data transfer may be initiated only when the bus is not busy.

\*The CSB (DB5) Pin must be setting to "VSS".

\* When IIC interface is selected, the DL register must be set to "1".

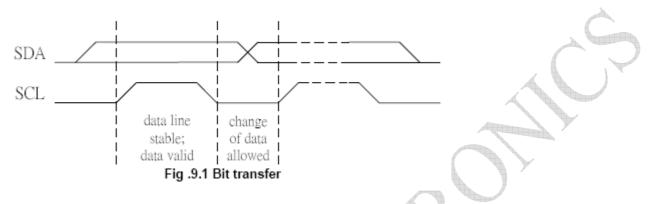

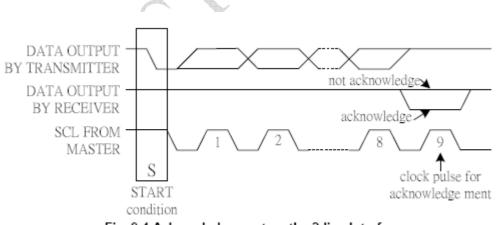

#### **BIT TRANSFER**

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the